Dit en d'autres termes, un même état des entrées peut faire apparaître des sorties différentes.

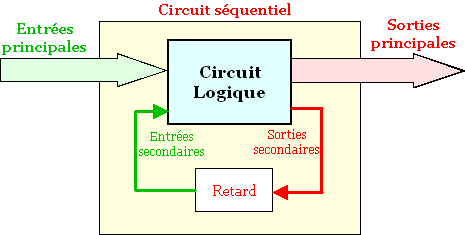

En logique séquentielle nous sommes donc amené à définir les entrées et sorties principales, celles qui sont en quelque sorte visibles de l'extérieur par l'utilisateur, et les entrées et sorties secondaires, internes au circuit et qui introduisent l'aspect temporel.

Les sorties secondaires sont en effet rebouclées sur les entrées principales à travers un bloc introduisant un retard t.

Examinons un circuit séquentiel à un instant t1 où l'état des entrées principales change et devient Ep(t1). Les sorties, principales et secondaires prennent une nouvelle valeur, Sp(t1) et Ss(t1). Puis les sorties secondaires étant rebouclées sur les entrées secondaires, ces dernières vont à nouveau changer d'état après le temps de transfert t.

Deux cas peuvent alors se présenter

:

- à t1+t les sorties restent

dans le même état qu'à t1 : on dit que le

circuit est dans un état stable.

- A t1+t les sorties changent de nouveau

d'état : on dit que le circuit est dans un état

instable.

Le temps est donc un paramètre essentiel à prendre en compte dans l'étude des circuits séquentiels.

La contre-réaction des

sorties secondaires vers les entrées peut se faire de deux façons

:

- seuls les temps de propagation des circuits fixent la valeur de la constante

de temps de retard t. Cette constante de temps ne pouvant être exactement

la même pour tous les circuits, le fonctionnement global se fera de

façon asynchrone. Tous

les états ne changent pas simultanément.

- Le bouclage des sorties vers les entrée se fait au rythme d'une

horloge de commande. Cette horloge synchronise les retards. Le fonctionnement

du circuit est synchrone.