Liaison HCMOS ---> TTL

Cas

du niveau BAS :

Une sortie HCMOS au niveau bas atteindra au maximum 0,1 V, et pourra absorber

4 mA (voir

la famille HCMOS).

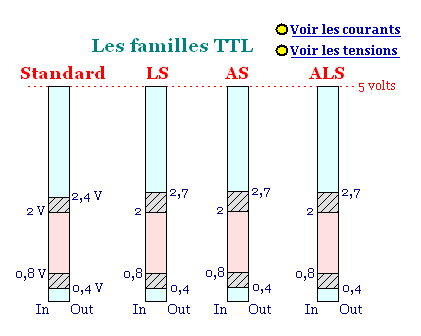

Une entrée TTL voit un niveau bas tant que le niveau ne dépasse

pas 0,8 volt, et débite au maximum 2 mA (voir

les familles TTL).

La compatibilité en tension ne pose donc pas de problème au niveau bas, mais il y a un problème d'absorption du courant. La sortance est en effet de 2 si rien n'est fait. Il est possible d'augmenter la sortance en placant des portes HCMOS en parallèle, au détriment du coût de l'ensemble, ou de changer sensiblement de technologie (1).

Cas

du niveau HAUT :

Une sortie HCMOS au niveau haut atteindra au minimum 4,9 V, et pourra

fournir entre 4 mA (voir

la famille HCMOS).

Une entrée TTL voit un niveau haut tant que le niveau ne tombe

pas sous 2 volts, et absorbe au maximum 200 mA

(voir

les familles TTL).

La compatibilité en tension ne pose donc pas de problème au niveau haut, et la sortance est égale à 20 portes dans le pire des cas.

(1) Dans le cas ou l'on doit commander plusieurs entrées TTL avec une seule porte MOS, la solution idéale est d'utiliser une porte en technologie BiCMOS, à sortie bipolaire, ou bien d'utiliser des portes TTL en technologie Low Power Schottky.

On constate que pour chaque technologie, les problèmes d'interfaçage sont différents puisque ni les niveaux de tension en entrée et en sortie, ni les niveaux de courants ne sont les mêmes (sauf exceptions). Il faudra donc prendre soin de bien vérifier que la liaison entre deux portes de technologies différentes ne pose pas de problème.