Les familles ECL

Cette famille logique introduite initialement par Motorola (familles MECL), a également été développée par Fairchild en trois groupes 10k, 100k et 1M.

Les familles ECL (Emetter Coupled Logic) sont des familles logiques très rapides, à étage d'entrée différentiel, car leurs transistors ne sont jamais saturés.

Ces familles qui possèdent une bande passante de 50 Mhz peuvent donc avantageusement remplacer la TTL pour toutes les applications de transmissions.

Les familles ECL sont alimentées entre 0 et -5,2 volts.

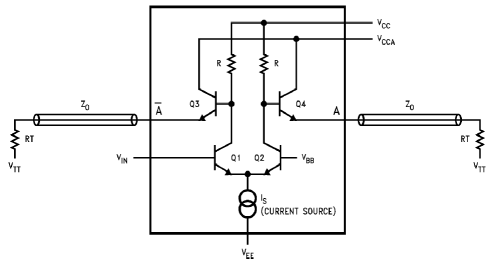

L'étage d'entrée différentiel reçoit sur une entrée un potentiel de référence VBB de -1,32 V, l'autre entrée étant l'entrée logique. La tension d'entrée différentielle détermine lequel des deux transistors Q1 ou Q2 va conduire pour laisser passer le courant constant Is.

Si l'entrée Vin est au niveau bas de -1,75 V (valeur typique), alors Q1 se bloque et Q2 est passant, amenant ainsi A au niveau Bas, et bien entendu son complément au niveau Haut.

Si l'entrée Vin est au niveau haut de -0,97 V (valeur typique), alors c'est Q1 qui conduit et Q2 qui se bloque. La sortie A passe alors au niveau Haut.

Le courant Is étant constant, il n'y a pas de pointes de courant dans l'alimentation même pendant les commutations, contrairement à la famille TTL.

Les circuits de la famille ECL ont en effet deux sorties complémentaires en mode collecteur commun.

Les temps de transfert vont de 3 ns pour la première famille MECL à moins de 1 ns pour la MECL III, au prix d'une forte consommation (50 mW par porte environ) et d'un prix très élevé en raison leur faible diffusion.